随着数字信号处理技术、数字电路工作速度和系统灵敏度等要求的不断提高,对高速、高精度的ADC指标提出了更高的要求。比如移动通信、图像采集等应用领域中,一方面要求ADC有高的采样率以采集高带宽的输入信号,一方面又要有高的位数以分辨细微的变化。因此,保证ADC在高速采样情况下的精度是一个很关键的问题。ADC性能好坏直接影响整个系统性能的好坏, ADC的性能测试变得十分重要。

目前的实时信号处理机要求ADC尽量靠近视频、中频甚至射频,以获取尽可能多的目标信息。因而,ADC的性能好坏直接影响整个系统指标的高低和性能好坏,从而使得ADC的性能测试变得十分重要。

ADC芯片的性能测试是由芯片生产厂家完成的,需要借助昂贵的半导体测试仪器, 但是对于板级和系统级的设计人员来说, 更重要的是如何验证芯片在板级或系统级应用上的真正性能指标。

ADC静态测试的方法已研究多年,国际上已有标准的测试方法,但静态测试不能反映ADC的动态特性,因此有必要进行动态测试。

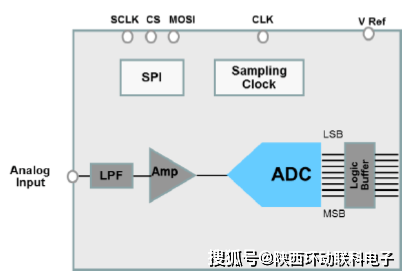

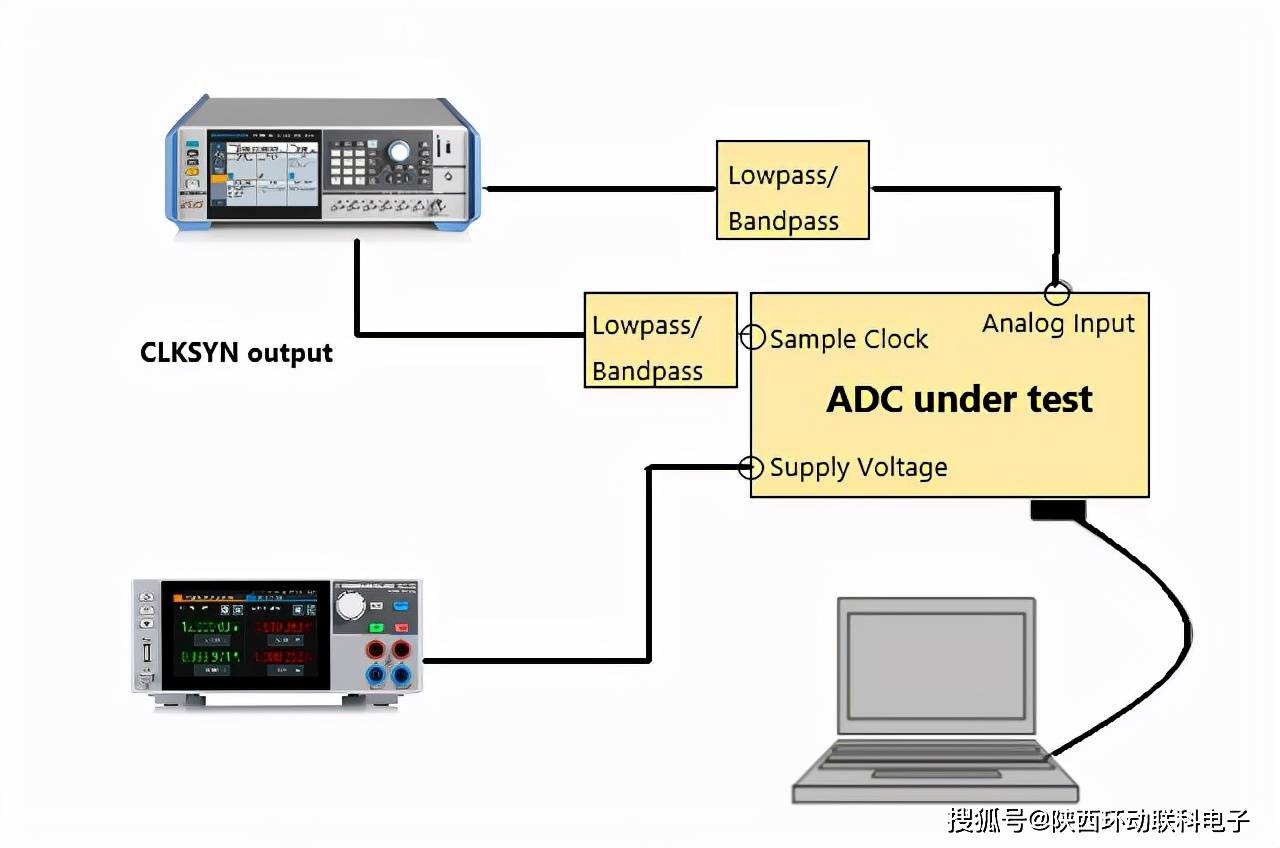

ADC典型接口如下图所示,

包括:

ADC静态指标:

ADC动态指标:

ADC测试可分为静态测试与动态测试,静态测试的方法已研究多年,国际上已有标准的测试方法,但静态测试不能反映ADC的动态特性,因此有必要进行动态测试。

挑战主要分为以下5点:

为确保系统正常运行,需流畅的电压为ADC和时钟供电。在现如今的ADC设计中,通常使用低压差 (LDO) 稳压器来提高电压的稳定性。

要求电源低纹波噪声和低电压偏差。

纹波噪声和串扰等电源完整性问题会严重影响ADC性能。

要求示波器及探头具备高灵敏度、高偏置与强大的FFT多域测量能力。

时钟性能对ADC十分关键。

要求时钟替代品相位噪声和抖动性能卓越,频谱纯度高,功率高

时钟抖动和频谱纯度会直接影响ADC的动态范围。

要求相位噪声分析仪灵敏度高、可测附加相位噪声、可进行频谱测量。

ADC性能参数直接影响系统整体性能。

要求测试分析仪频谱纯度高、带宽和EVM性能出众、触发精度高、解码功能速度快眼图和抖动分析功能全面。

针对以上挑战,罗德与施瓦茨提供的测试方案及优点如下:

采用R&S®NGM、R&S®NGL与HMP系列高性能/专业电源可向ADC传输流畅、稳定且精确的直流电源,该方案的优点包括:

采用R&S®RTO、RTE系列示波器与RT-ZPR电源轨探头测量电源完整性,该方案的优点包括:

高精度直流电压表 偏置范围±60V

硬件准实时FFT 时域、频域同时分析

采用R&S®SMA100B和R&S®SMB100A信号源提供处于不同性能范围的时钟替代品,该方案的优点包括:

全无损耗电子衰减器 不同性能级别多个选项

高输出功率 补偿损耗 SMAB-B29时钟源次级输出

方案1:采用R&S®FSWP相位噪声分析仪和VCO测试仪进行时钟验证;

方案2:采用R&S®FSW、R&S®FSVA、R&S®FSV和R&S®FPS频谱分析仪及其相位噪声测量功能进行时钟验证。

该组方案的优点包括:

采用R&S®SMA100B、R&S®SMBV100A和R&S®SMW200A进行性能特性测试,该方案的优点包括:

传统方案是给ADC输入端口一个理想模拟信号,给时钟端口一个理想采样信号,以及相应的直流电源、滤波器等附件。然后对ADC转换以后的数据进行采集和分析。信号源的信号质量要超过待测ADC。ADC的性能测试需要多台高性能模拟信号源的配合并用软件对测结果进行分析。

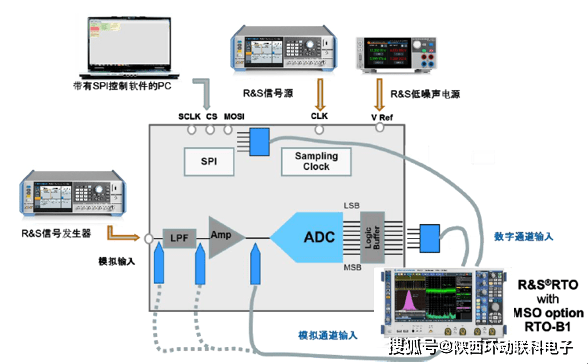

测试系统包括四台仪器:一台信号源SMA100B作为产生高精度、高纯净度的正弦波给待测ADC作为源输入,ADC在另外一台信号源SMA100B提供的采样时钟的控制下对此正弦波进行采样,变换后的结果用软件或者RTO示波器逻辑分析仪选件采集下来。

两台SMA100B信号源把10MHz的参考频率同步起来,这样两台信号源的相位噪声在环路带宽内(1Hz-100Hz)具有相关性,不会影响测试结果。

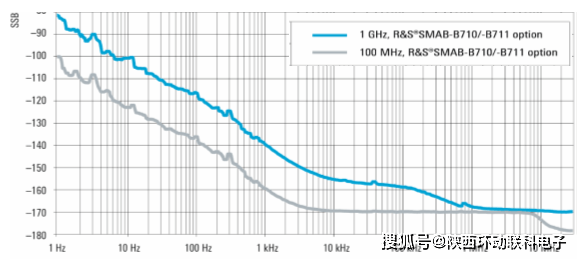

SMA100B信号源的相位噪声极低,产生的正弦波的质量极高,如下图的SSB指标所示,1GHz频率的信号的相位噪声可低至-155dBc(10k offset).

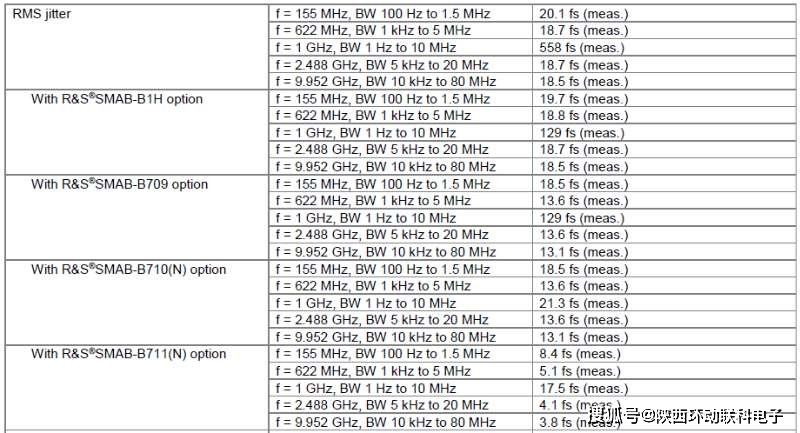

时钟的抖动对于测量结果的影响非常大,测试中需要低jitter信号发生器来产生ADC的采样时钟。SMA100B作为时钟的提供源,其jitter指标也相当优异,可以控制在fs量级。

ADC转换后的数字结果通过电脑软件或者示波器逻辑分析选件采集下来进行分析。通常厂商提供某款ADC的评估板,该评估板上的USB接口可以将结果传回电脑软件进行分析。如果采用示波器逻辑分析选件,该选件工作在状态采样模式,需要使用的通道数取决于ADC的位数,状态采样率取决于 ADC的采样率,存储深度取决于采样率和要分析的频率分辨率。

如果ADC的应用不做降采样应用(IF数字下变频),可采用如下方案节省成本。R&S的模拟信号源SMA100B是可同时提供模拟信号输出和采样时钟输出的单台仪表,可节约一台信号源作。

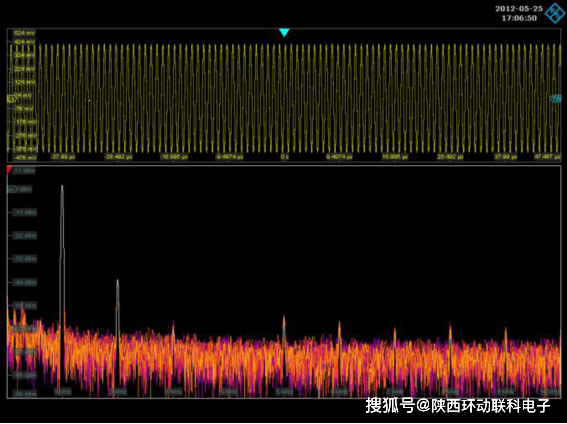

使用示波器对输入信号做FFT分析,了解信号在不同阶段的性能,包括:

RTO示波器的优势:

测量分析如下图所示:

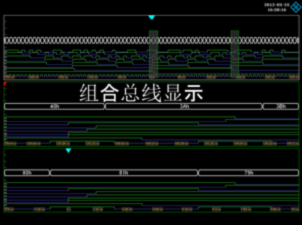

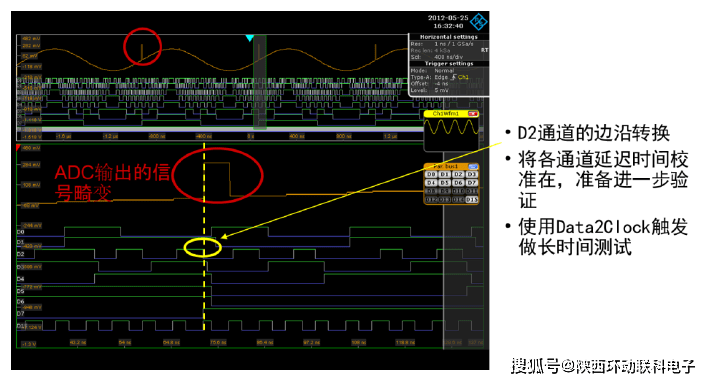

将ADC输出通过探头连接到示波器数字输入通道,配置各通道的总线定义,测量并验证输出数据的正确性,分析信号质量。

RTO示波器优势:

设置截图如下:

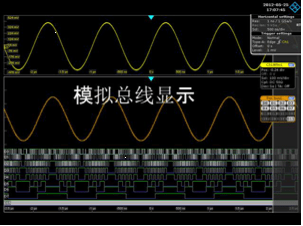

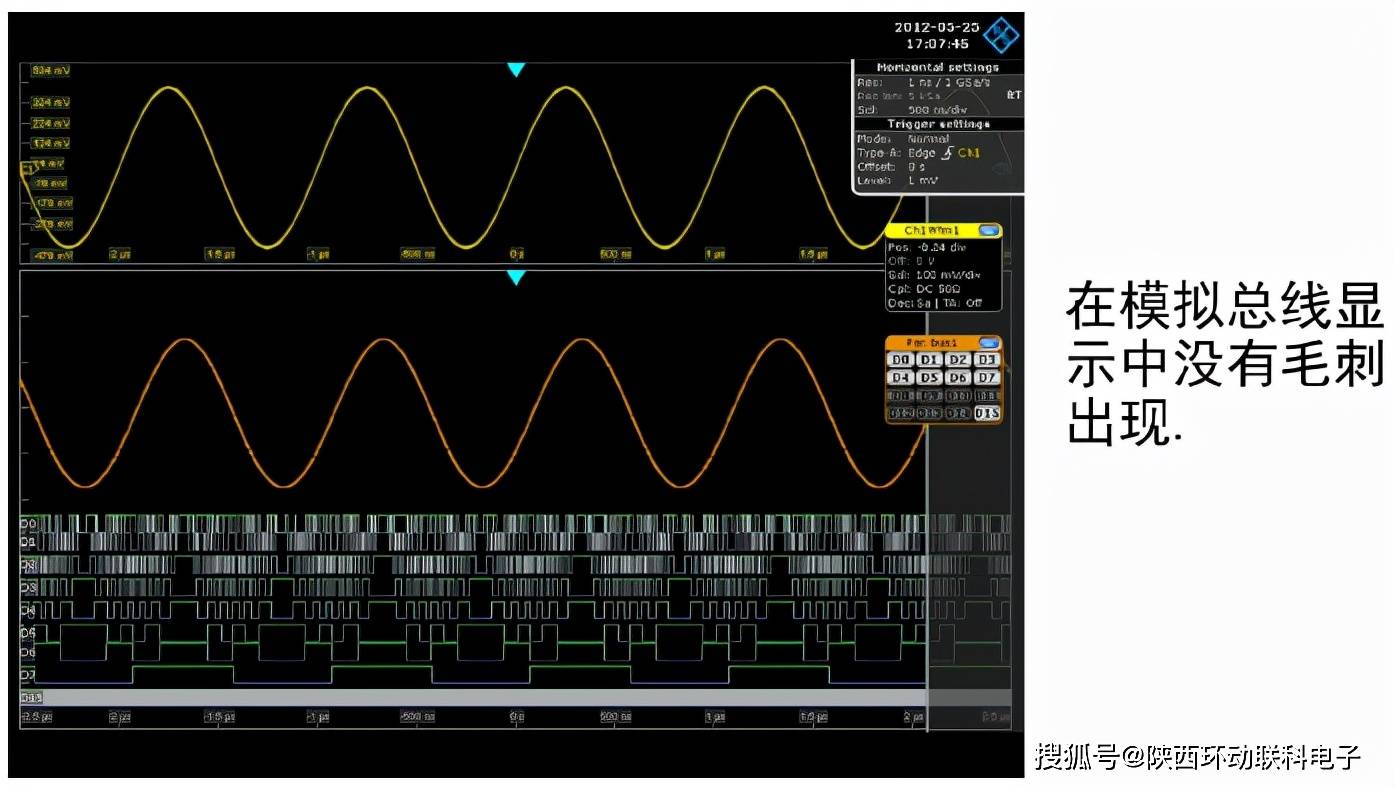

用Analog Bus显示分析输出信号质量。 传统的总线解码为组合总线显示,是将一定时间的数据汇总显示。而RTO创新的模拟总线显示Analog bus显示总线数据代表的模拟波形,这样 输入和输出信号更容易对照比较。如下图所示:

分析ADC输出信号(可通过MATLAB分析):保存模拟总线波形 --> 执行FFT和对应的频谱测量(FFT需要重新采样加强定时准确度) --> 将输入和输出信号关联测试ADC的性能。

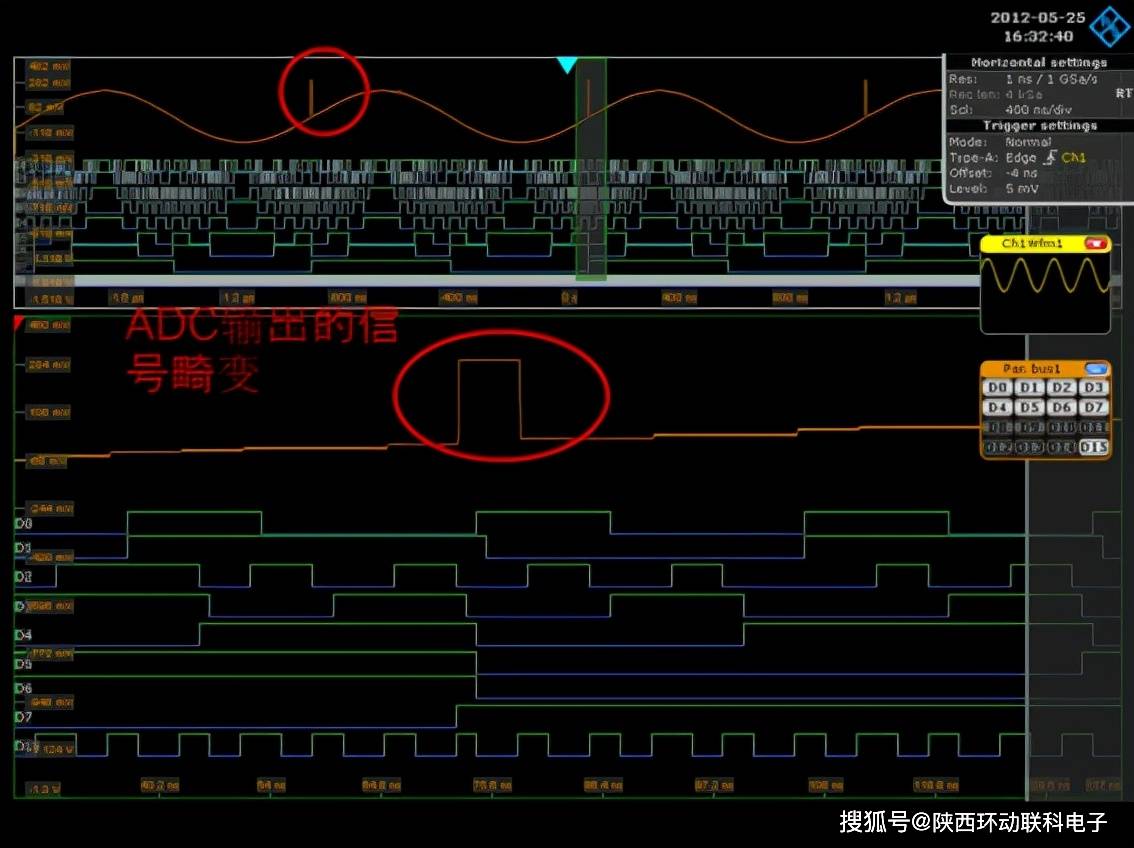

对输出信号进行调试。模拟总线显示有助于发现信号畸变,如下图:

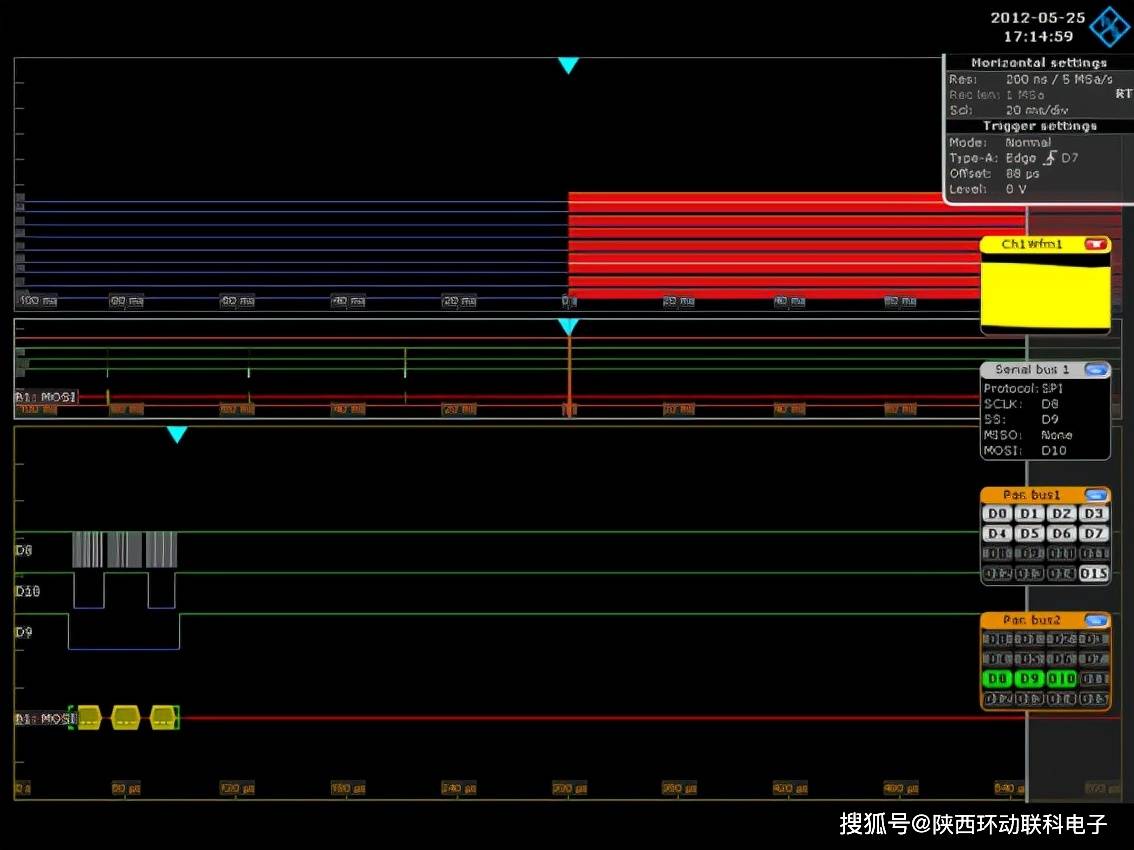

使用示波器数字通道连接SPI接口,使用SPI协议解码,设置触发于SPI “帧起始”。测量SPI指令下达到ADC工作的延迟时间。

RTO示波器的优势:

测量结果如下图:

综上所述,面对突飞猛进的ADC需求与ADC技术,罗德与施瓦茨为您提供最优测量仪器与解决方案,助您获得简便的测试过程与精确的测试结果。

关于罗德与施瓦茨

罗德与施瓦茨公司作为一家独立的国际性科技公司,为专业用户开发、生产以及销售创新的通信、信息和安全产品。公司主要业务领域包括测试与测量、广播电视与媒体、航空航天|国防|安全、网络信息安全并覆盖多个不同行业及政府市场分支。截止到2019年6月30日,罗德与施瓦茨公司员工人数约为12,000名。公司总部设在德国慕尼黑。全球范围内,公司在70多个国家设有子公司并在亚洲和美国设有区域中心。

Copyright © 2022-2023 深圳市中科测仪科技有限公司 版权所有 备案号:粤ICP备2021017612号-1